myPinballs

Active member

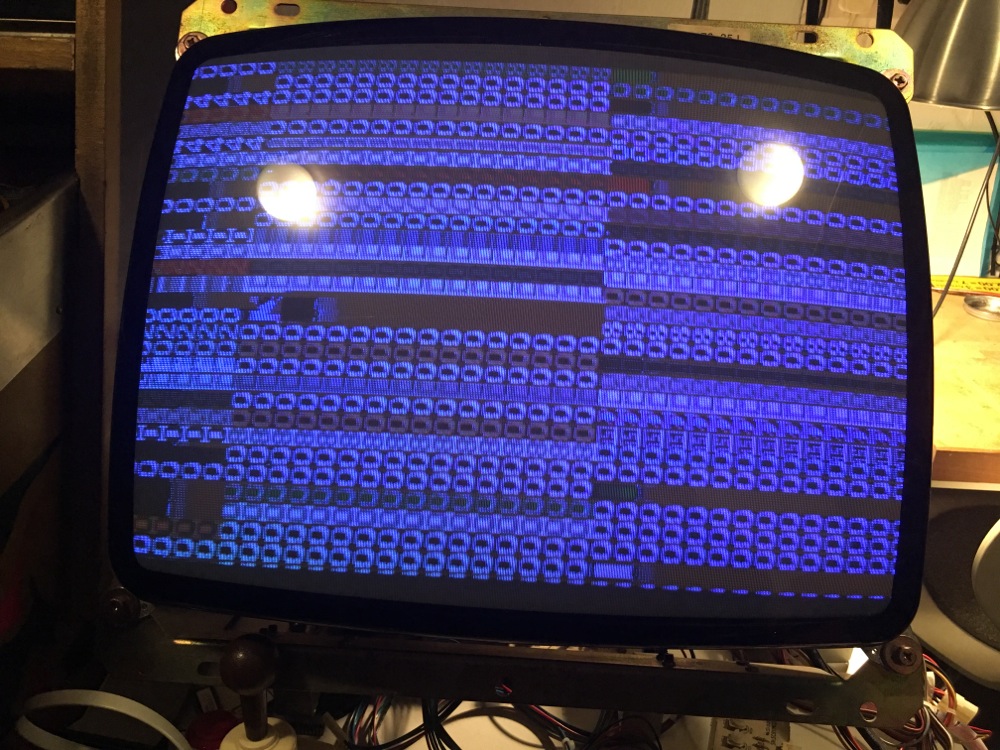

From my board repair i'm still stuck on this screen

Though i have worked out that i can change some of the characters on screen by shorting various lines of the data buffers for the foreground and background ram. So i need to think more as to why its not all zeros.

Also, i don't get a solid picture all the time still, sometimes its not synced and it just lines or noise. I think i may have worked out the likely culprit here as can tell what isn't pulsing when the image disappears.

Traced it to the horizontal section chips 1F & 2F and 1D which i think one or more are failing. They are the starting point for the vertical section line clock. They are 74LS669 ics so ordering some to replace and try out shortly.

Fingers crossed.

myPinballs2018-01-17 12:26:06

Though i have worked out that i can change some of the characters on screen by shorting various lines of the data buffers for the foreground and background ram. So i need to think more as to why its not all zeros.

Also, i don't get a solid picture all the time still, sometimes its not synced and it just lines or noise. I think i may have worked out the likely culprit here as can tell what isn't pulsing when the image disappears.

Traced it to the horizontal section chips 1F & 2F and 1D which i think one or more are failing. They are the starting point for the vertical section line clock. They are 74LS669 ics so ordering some to replace and try out shortly.

Fingers crossed.

myPinballs2018-01-17 12:26:06